China’s RISC-V Server CPU Push: Redefining Global Computing Through Open Hardware

The evolution of global processor architecture has long been dominated by two prevailing paradigms: the proprietary x86 instruction set architecture (ISA), led by Intel and AMD, and the increasingly influential ARM architecture, spearheaded by companies such as Arm Ltd., Apple, and Qualcomm. These architectures have shaped the digital landscape for decades, powering everything from personal computers and smartphones to enterprise servers and supercomputers. However, a new force is emerging that threatens to upend the established order—RISC-V, an open-source instruction set architecture that promises to democratize the future of computing.

RISC-V, pronounced “risk-five,” originated as a research project at the University of California, Berkeley. Unlike its predecessors, RISC-V is built on an open standard, offering a modular and extensible architecture that allows companies, institutions, and even individuals to design and customize processors without paying licensing fees or adhering to rigid, vendor-controlled ecosystems. This open approach has captured the imagination of engineers, academics, startups, and now, entire nations. Among these, China has emerged as the most determined and strategically motivated player in the global RISC-V movement—particularly in the domain of server-class CPUs.

China’s pursuit of RISC-V technology for server applications is driven by a confluence of technical, economic, and geopolitical factors. The rise of open hardware coincides with China’s broader push to achieve technological self-sufficiency in critical sectors, especially semiconductors. This push has been sharply intensified by escalating tensions with the United States and the growing weaponization of supply chains. U.S. export controls and sanctions have limited China’s access to advanced semiconductors, Electronic Design Automation (EDA) tools, and even licensing rights to ARM-based and x86 cores. In this context, RISC-V represents more than a technical curiosity—it is a strategic lifeline.

By adopting RISC-V, China seeks to break free from the architectural monopolies that have long constrained its domestic semiconductor development. The open-source nature of RISC-V means that Chinese firms can build custom chips tailored to national priorities without incurring licensing costs or depending on foreign IP holders. For server-class processors, which are crucial to data centers, cloud infrastructure, AI model training, and national defense systems, this autonomy is both a technical necessity and a political imperative.

The push toward RISC-V server CPUs aligns with broader Chinese industrial policies such as “Made in China 2025” and the 14th Five-Year Plan, which emphasize innovation in high-performance computing, big data, AI, and quantum information sciences. Chinese tech giants such as Alibaba, Huawei, and Tencent are investing heavily in custom silicon initiatives, while government-backed institutions like the Chinese Academy of Sciences and top engineering universities are directing significant resources into RISC-V-based research and development. These efforts are supported by a burgeoning startup ecosystem, national-level semiconductor investment funds, and regional innovation zones tailored to fabless chip design.

Globally, the RISC-V movement has garnered support as an alternative to the increasingly restrictive licensing regimes of incumbent players. However, no other nation has embraced it as aggressively or as comprehensively as China. As a result, the development of RISC-V server CPUs within China has become a focal point not only for domestic innovation but also for international strategic analysis. If successful, these efforts could allow China to bypass traditional chokepoints in the semiconductor supply chain, while simultaneously reshaping global standards for processor design.

At the technical level, designing server-class CPUs using RISC-V poses formidable challenges. Unlike embedded systems or microcontrollers, server workloads require high-performance cores, sophisticated memory hierarchies, advanced vector processing units, and comprehensive security and virtualization features. China’s RISC-V server CPU developers must contend with these demands while simultaneously building out the broader software ecosystem—including compilers, operating systems, firmware, and performance optimization frameworks—that is essential for real-world deployment. Despite these hurdles, recent announcements and early prototypes suggest that China is making significant strides, with several organizations publicly committing to building high-core-count RISC-V chips for enterprise and cloud environments.

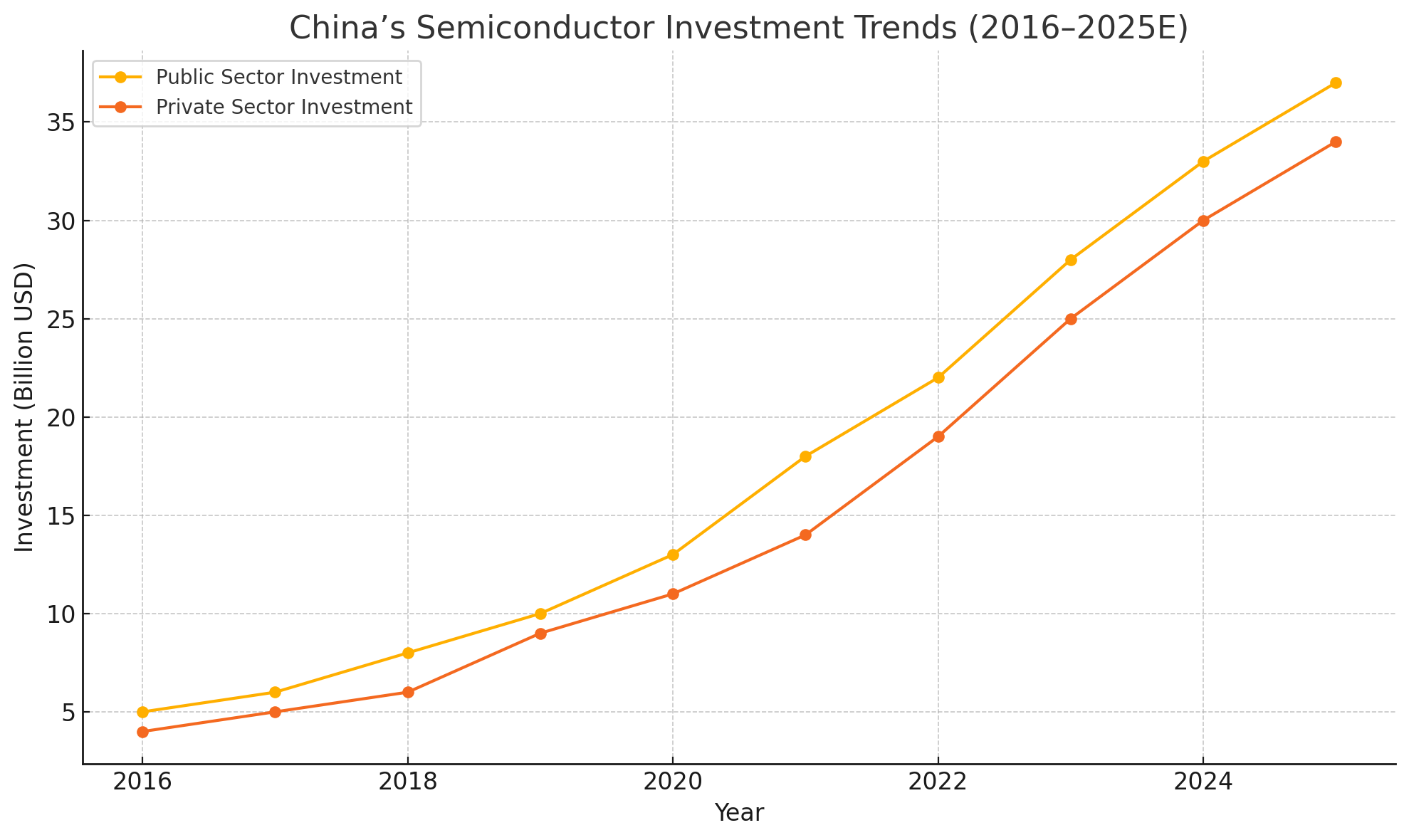

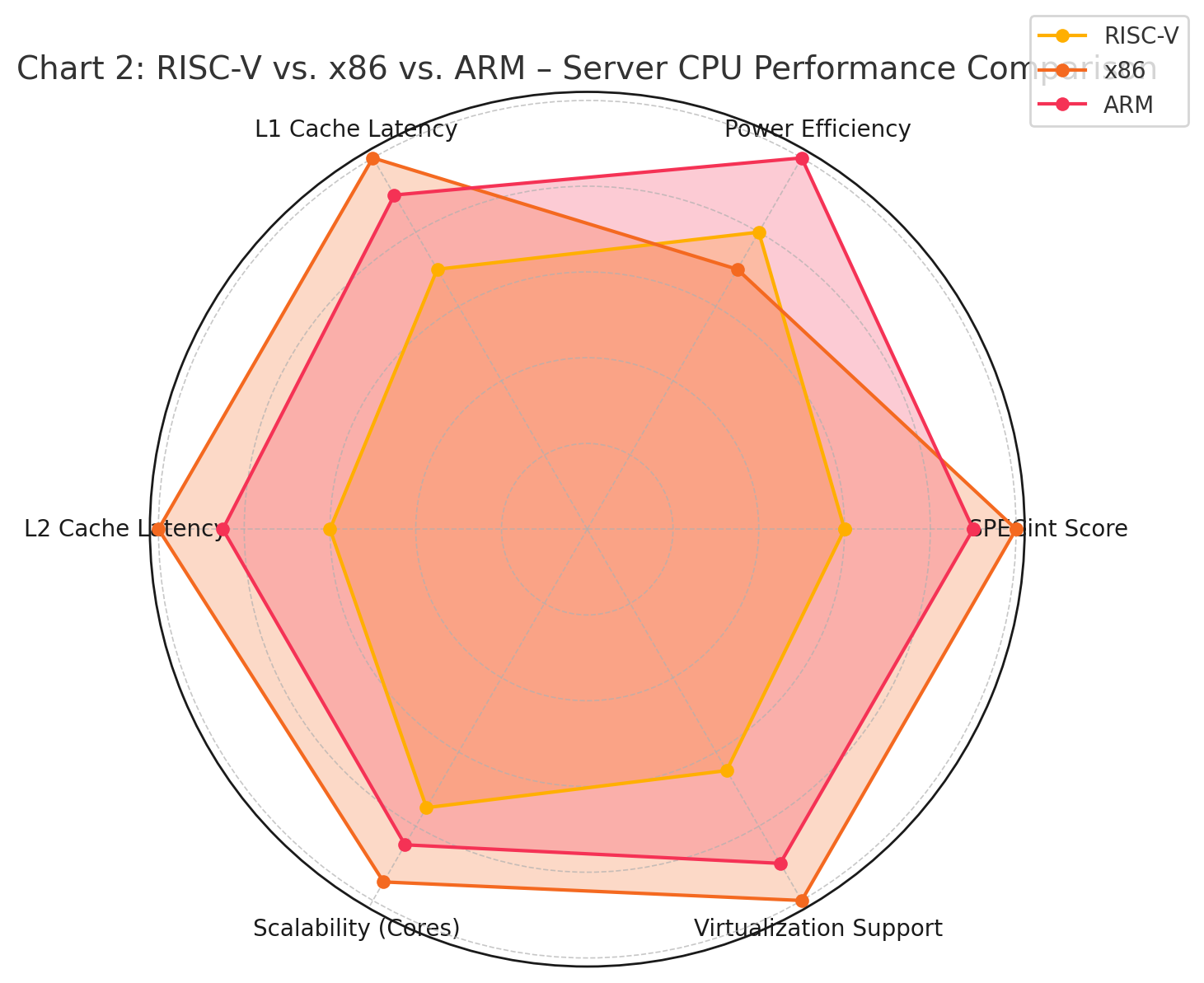

This blog post aims to provide a comprehensive and structured overview of China’s development of RISC-V server CPUs, analyzing the motivations, key players, technical achievements, and global implications of this fast-moving domain. The following sections will explore China’s national strategy for RISC-V, map out the emerging domestic RISC-V ecosystem, evaluate the technical and manufacturing bottlenecks, and assess how this trajectory fits into the broader landscape of global processor competition. We will also present two data-driven charts—one highlighting China's semiconductor investment trends and another comparing performance across leading CPU architectures—and a detailed table outlining major RISC-V server CPU projects currently under development within China.

Ultimately, the story of China’s RISC-V server CPU development is not just about chip design—it is about sovereignty, standard-setting, and systemic resilience. As the global technology order continues to fragment and as proprietary architectures increasingly become instruments of national strategy, open-source hardware like RISC-V offers an alternative vision—one rooted in collaboration, transparency, and self-determination. Whether this vision can translate into performance, scale, and market adoption remains to be seen, but one thing is certain: the world is watching.

The Rationale Behind China’s RISC-V Strategy

China's decision to embrace RISC-V as a cornerstone of its semiconductor strategy, particularly for server-class central processing units (CPUs), is neither incidental nor opportunistic. Rather, it is the result of a calculated national policy response to technological exclusion, increasing licensing costs, and a rapidly evolving geopolitical landscape. The country’s shift toward open-source processor architectures stems from a multi-dimensional rationale that spans economic sovereignty, industrial competitiveness, technological innovation, and long-term security imperatives.

At the center of this strategic pivot lies the escalating tech war between the United States and China, a conflict that has redefined the contours of global supply chains and disrupted traditional access to semiconductor intellectual property. Beginning in 2019, the U.S. government imposed a series of export controls and blacklists targeting Chinese technology firms, most notably Huawei and Semiconductor Manufacturing International Corporation (SMIC). These restrictions curtailed access to advanced chipmaking equipment, Electronic Design Automation (EDA) tools, and, crucially, foreign-owned processor architectures such as x86 (Intel, AMD) and ARM (Arm Ltd., a subsidiary of SoftBank and now publicly traded).

The licensing models of both x86 and ARM architectures have long placed constraints on China’s ability to develop sovereign, high-performance computing capabilities. The x86 architecture is tightly controlled by U.S.-based companies under long-standing cross-licensing agreements. While ARM has been more widely available under commercial licensing terms, its strategic alignment with Western regulatory regimes makes it susceptible to geopolitical influence. For example, in recent years, Arm Ltd. has faced regulatory pressure from U.S. and U.K. authorities when attempting to license its most advanced designs to Chinese firms.

These conditions have heightened the urgency of technological self-reliance in Beijing. In response, the Chinese government has significantly increased its investment in domestic semiconductor innovation through initiatives like the National Integrated Circuit Industry Investment Fund (commonly known as the “Big Fund”) and strategic roadmaps embedded in the 14th Five-Year Plan and “Made in China 2025.” These policy instruments prioritize independence in key technologies, including CPU design, advanced node fabrication, and high-performance computing infrastructure.

Against this backdrop, RISC-V emerges as an ideal candidate to fulfill China’s ambitions. Unlike proprietary ISAs, RISC-V is governed by an open-source licensing model under the auspices of RISC-V International, a global nonprofit consortium. It permits any organization to implement the architecture without paying royalties, applying for licenses, or adhering to vendor-specific restrictions. For Chinese developers, this model offers unmatched flexibility and freedom from political risk. Furthermore, RISC-V’s modular structure allows implementers to customize processor designs to suit specific application domains—from low-power IoT devices to high-performance servers.

China's embrace of RISC-V is also driven by a desire to leapfrog legacy constraints and innovate at the architectural level. While x86 is burdened by decades of backward compatibility and ARM increasingly faces fragmentation challenges due to vendor-specific extensions, RISC-V offers a clean slate. This facilitates architectural experimentation, performance tuning, and domain-specific optimization—particularly valuable for AI acceleration, machine learning inference, and edge computing, all of which are strategic growth areas for China.

Institutional support has further accelerated the RISC-V ecosystem within the country. Leading universities such as Tsinghua University and the Institute of Computing Technology (ICT) at the Chinese Academy of Sciences have launched open-source RISC-V projects (e.g., XiangShan and NutShell) aimed at educating the next generation of chip designers and producing proof-of-concept server-class CPUs. Concurrently, state-owned enterprises and technology conglomerates like Alibaba (via its T-Head Semiconductor Division) and Huawei (through its openEuler and HarmonyOS initiatives) are integrating RISC-V into both silicon and software layers of their ecosystems.

China's regional governments have also joined the national effort by establishing semiconductor innovation hubs, often offering subsidies, tax incentives, and access to fabrication facilities for RISC-V startups. Municipalities such as Shanghai, Shenzhen, and Chengdu have attracted a growing number of fabless design houses dedicated to RISC-V development. These firms are supported by government-sponsored accelerators and venture capital vehicles aligned with national priorities.

Beyond hardware, China is also cultivating a software ecosystem compatible with RISC-V, recognizing that chip innovation is meaningless without a robust platform for execution. Organizations such as PLCT Lab and the China RISC-V Alliance are developing open-source compilers (e.g., GCC, LLVM), libraries, operating system ports (Linux, RTOS), and hypervisors to enable deployment in real-world server environments. Initiatives like Alibaba’s Xuantie SDK and Huawei’s integration of RISC-V support into its openEuler OS are representative of a broader trend toward domestic software-software co-optimization.

Internationally, China is also seeking greater influence in the standardization process of the RISC-V ISA. While RISC-V International remains a global body with members across academia, industry, and national labs, China has significantly expanded its presence within the consortium. Several working groups are now led by Chinese engineers, and proposals from Chinese institutions are shaping the direction of future RISC-V extensions. This is a deliberate effort to avoid repeating the mistakes of the past, where China was often relegated to a passive consumer role in standards development dominated by Western companies.

Moreover, the Chinese government views RISC-V as a neutral, apolitical technology base that aligns with its broader advocacy for technological multipolarity and digital sovereignty. In official discourse, RISC-V is frequently cited as an example of how open-source collaboration can lead to shared innovation without being beholden to specific geopolitical blocs. This narrative not only reinforces domestic morale but also appeals to other nations seeking to diversify their technology stack away from Western-centric architectures.

In summary, China’s strategic rationale for pursuing RISC-V server CPU development is grounded in both necessity and opportunity. Necessity, because geopolitical constraints and IP restrictions have made continued reliance on foreign architectures untenable. Opportunity, because RISC-V offers a customizable, royalty-free path to technological leadership that aligns with the country's long-term goals in AI, HPC, and cloud computing. Through a combination of policy instruments, institutional coordination, financial investment, and global standard-setting, China is positioning itself as a dominant force in the emerging open hardware movement.

China’s Emerging RISC-V Server CPU Ecosystem

The advancement of RISC-V server CPUs in China is not merely a matter of national policy or strategic doctrine—it is also a rapidly materializing technological ecosystem composed of commercial enterprises, academic institutions, and government-backed research entities. These stakeholders are collectively laying the groundwork for what could become one of the world’s most expansive and self-reliant RISC-V development environments, tailored specifically to the demands of high-performance computing (HPC), enterprise servers, cloud platforms, and AI infrastructure.

At the heart of this ecosystem is a growing cadre of domestic semiconductor companies that are actively designing and prototyping RISC-V-based CPUs for server-class applications. These firms vary widely in terms of size, maturity, and specialization, but all share a common objective: to develop competitive, domestically engineered alternatives to x86 and ARM processors for datacenter and edge workloads. Some companies are wholly private, while others are affiliated with state-owned enterprises or receive preferential support from regional and national authorities.

Leading Industry Players and Research Institutions

Alibaba Group’s T-Head Semiconductor Division (also known as Pingtouge) is arguably the most visible commercial entity championing RISC-V development in China. Since the debut of its Xuantie processor line, Alibaba has emerged as a leader in both high-performance RISC-V chip design and ecosystem enablement. The Xuantie C910, a 64-bit superscalar processor, demonstrated the feasibility of using RISC-V cores for more complex computing tasks. While primarily designed for edge and embedded applications, T-Head has signaled intentions to scale the architecture upward for cloud-native workloads and server use cases through more advanced designs such as the Xuantie C920.

Another pivotal contributor is XiangShan, a research initiative under the Institute of Computing Technology (ICT) at the Chinese Academy of Sciences. XiangShan is a fully open-source, high-performance RISC-V CPU project aimed at demonstrating competitive execution pipelines, cache hierarchies, and out-of-order scheduling mechanisms. The project’s roadmap includes multi-core, server-class implementations designed to match or exceed ARM Cortex-A performance in key benchmarks. XiangShan’s first two iterations—Yanqihu and Yuki—are already publicly available for evaluation and community collaboration, with active participation from universities and commercial partners.

StarFive, an emerging fabless semiconductor company based in Nanjing, represents another important node in the Chinese RISC-V server chip landscape. While StarFive gained attention for its VisionFive single-board computers (SBCs), it has also developed more robust platforms such as the Dubhe processor, an eight-core 64-bit RISC-V chip targeting edge and lightweight server environments. Although not yet designed for high-performance workloads, Dubhe serves as a stepping stone toward more scalable architectures.

Other notable initiatives include the Wujian platform, jointly promoted by T-Head and local governments, and semi-autonomous regional R&D programs that focus on customized RISC-V cores for vertical applications like smart cities, transportation, and public sector cloud services. Additionally, high-tech zones in Shanghai, Shenzhen, Chengdu, and Hangzhou are incubating startup ecosystems specifically focused on RISC-V-based server, storage, and networking silicon.

Notable Chinese RISC-V Server CPU Projects and Specifications

Software Stack and Ecosystem Integration

A defining characteristic of server-grade CPU development is the integration of software layers that can extract full utility from the underlying hardware. In China, significant progress has been made to develop and port essential components of the RISC-V software stack, including compilers, toolchains, debuggers, and operating systems.

The PLCT Lab (Programming Language and Compiler Technology Lab) under the Institute of Software, Chinese Academy of Sciences, is instrumental in maintaining RISC-V support across major compiler toolchains like GCC and LLVM. Additionally, performance libraries such as OpenBLAS, TensorFlow Lite, and PyTorch are being adapted to support RISC-V ISA extensions, including vector processing and matrix acceleration.

On the operating system front, multiple Linux distributions have either added or committed to RISC-V support. These include mainstream platforms such as Fedora, Debian, and Ubuntu, as well as domestic initiatives like openKylin, UnionTech UOS, and openEuler—the latter of which is maintained by Huawei. Huawei’s contribution is particularly notable for its effort to provide a full-stack, enterprise-ready server OS with RISC-V compatibility.

The open-source nature of many of these contributions has led to an environment of rapid iteration and cross-pollination. University students, hobbyists, and commercial developers often co-develop features, submit patches, and test experimental configurations on shared hardware platforms such as VisionFive boards, FPGA emulators, and custom development kits provided by Alibaba and StarFive.

Cloud Integration and Datacenter Use Cases

While most of the current RISC-V chips in China are still in the prototyping or edge deployment phase, preliminary integration into cloud-native environments has already begun. Alibaba Cloud has launched internal R&D programs to test RISC-V-powered nodes for lightweight microservices, container orchestration, and inference acceleration in isolated, low-risk environments. Similarly, Baidu and Tencent have expressed interest in incorporating RISC-V CPUs into internal projects focused on object storage, security analytics, and low-power compute offloading.

The modular design of RISC-V also enables China’s hyperscale cloud providers to tailor instruction set extensions for specific datacenter workloads, such as encryption, compression, or real-time analytics. This level of customization—combined with tight integration into software-defined infrastructure—creates opportunities for optimization that traditional x86-based systems cannot offer without significant licensing and engineering overhead.

Furthermore, several state-sponsored sovereign cloud programs are exploring the use of RISC-V-based server chips to establish technology-independent digital infrastructure for public sector workloads. These initiatives are seen as critical to long-term national security goals and are likely to become early adopters of RISC-V chips once performance and software maturity reach acceptable thresholds.

Incubation and Collaboration Models

Another notable feature of China’s RISC-V ecosystem is the institutional support for incubation and collaboration. Industry-academic partnerships are commonplace, with many projects receiving joint funding and technical assistance from universities, government agencies, and venture capital arms of large corporations. Hackathons, bootcamps, and IP-sharing agreements are used to accelerate time-to-market and reduce duplication of effort.

The government has also played a coordinating role by promoting open standards adoption, establishing national benchmarks, and funding open-source repositories. Organizations such as the China RISC-V Industry Consortium and the RISC-V Alliance of China are actively aligning domestic efforts with international best practices while lobbying for the inclusion of Chinese-developed extensions into the global RISC-V ISA.

Technical Challenges and Bottlenecks

While China’s RISC-V server CPU ecosystem is progressing rapidly, its development is constrained by a series of complex technical, logistical, and infrastructural challenges. These bottlenecks are not unique to China but are significantly amplified by the country’s reliance on domestic resources in the face of geopolitical restrictions. Addressing these limitations is critical if Chinese RISC-V chips are to compete with entrenched architectures like x86 and ARM in server-class performance and reliability.

Performance Parity with x86 and ARM

The most immediate and formidable challenge facing China’s RISC-V server CPU developers is achieving performance parity with established processor architectures. Server-class workloads—such as virtualization, AI inference, real-time analytics, and database management—demand a level of sustained computational throughput that current RISC-V implementations have yet to deliver.

Leading x86 chips from Intel and AMD offer decades of cumulative performance optimization across cores, interconnects, memory controllers, and instruction-level parallelism. Similarly, ARM-based server processors—particularly those from Ampere, Amazon (Graviton), and NVIDIA—are benefiting from years of ecosystem tuning and have demonstrated compelling performance-per-watt metrics in datacenter environments.

Chinese RISC-V server CPUs, in contrast, are still in early development. Projects like Alibaba’s Xuantie C920 and XiangShan’s Yuki are promising from a microarchitectural standpoint but remain unproven at scale. Initial benchmarking, when available, indicates that these chips trail current-generation ARM and x86 processors in key metrics such as SPECint2006 scores, memory latency, and cache coherence efficiency. Moreover, limited access to advanced silicon process nodes further hinders the ability to close this performance gap in the near term.

Software Ecosystem Maturity

Another fundamental bottleneck is the relative immaturity of the RISC-V software ecosystem for enterprise-grade computing. While RISC-V has achieved considerable progress in compiler support, operating system compatibility, and open-source development tools, many enterprise workloads rely on proprietary software stacks, optimized runtime environments, and extensive backward compatibility—features that are tightly integrated with the x86 or ARM instruction sets.

Operating system support for RISC-V is advancing, with Linux distributions such as Debian, Fedora, and Ubuntu maintaining experimental or mainline ports. However, server-grade operating systems like Red Hat Enterprise Linux (RHEL), SUSE Linux Enterprise Server (SLES), and Windows Server do not yet support RISC-V, limiting deployment in enterprise environments.

Middleware, hypervisors, container orchestration frameworks (e.g., Kubernetes), and database engines (e.g., PostgreSQL, MySQL, Oracle) require significant optimization to fully leverage RISC-V’s capabilities. Without full ecosystem parity, the theoretical performance of RISC-V hardware remains difficult to realize in production environments.

Furthermore, enterprise IT teams have spent decades building operational expertise around x86 and ARM platforms. Transitioning to RISC-V would require retraining, process revalidation, and application compatibility testing—factors that introduce additional barriers to adoption.

Toolchain and Development Ecosystem

High-performance server chip development relies heavily on robust toolchains, including compilers, debuggers, profilers, verification frameworks, and simulation tools. While open-source options like GCC and LLVM support RISC-V, they lag behind commercial tools in performance optimization, automated tuning, and cross-architecture profiling.

China’s domestic EDA tool providers—such as Empyrean Technology and Primarius—are growing in capability but are not yet able to fully replace the advanced offerings from Cadence, Synopsys, and Siemens EDA, particularly for sub-10nm process nodes. Given that the U.S. government has imposed export restrictions on these tools to Chinese firms, local alternatives are essential but still under development.

The lack of access to state-of-the-art design tools not only affects the time-to-market for RISC-V chips but also impedes design verification and validation, both of which are critical for reliability in server applications. Bugs or inefficiencies introduced during early design stages may go undetected, leading to degraded performance or critical failures under load.

Advanced Node Fabrication Limitations

Fabrication remains a structural bottleneck in China’s domestic CPU development. High-performance processors require cutting-edge manufacturing nodes (e.g., 7nm, 5nm, or below) to meet the power, area, and thermal requirements of modern servers. However, China currently lacks the ability to manufacture chips at these advanced nodes domestically.

SMIC, China’s most advanced foundry, has demonstrated capabilities down to the 7nm node using Deep Ultraviolet Lithography (DUV), but yields are reportedly low, and mass production remains uncertain. Due to export restrictions, SMIC lacks access to Extreme Ultraviolet Lithography (EUV) machines from ASML, which are essential for efficient production at 5nm and below.

Consequently, Chinese RISC-V developers must either design chips for mature nodes (12nm or 28nm), which limits performance and energy efficiency, or rely on overseas fabs for small-volume prototypes—an approach that introduces supply chain complexity and strategic vulnerabilities.

Interoperability and Compatibility Challenges

In the server environment, interoperability is paramount. Enterprise servers are seldom deployed in isolation—they must integrate with storage systems, networking infrastructure, virtualization layers, and orchestration platforms. RISC-V’s relative novelty means that driver support, I/O standards, and peripheral compatibility are still being developed.

For example, PCIe support, DDR5 memory controllers, high-speed Ethernet interfaces, and hardware virtualization extensions are all in varying stages of development across different RISC-V projects. The fragmentation in implementation could lead to incompatibility across systems and make standardized deployment more difficult.

Moreover, legacy application compatibility is a concern. Enterprises typically maintain critical applications written and optimized for x86 over many years. Porting these applications to RISC-V is not a trivial endeavor—it requires recompilation, regression testing, and in some cases, code refactoring. Without a seamless migration path, adoption is likely to remain limited to greenfield deployments or niche verticals.

Security and Reliability Concerns

Security is a foundational requirement for server-grade processors. Incidents like Spectre, Meltdown, and recent firmware-based exploits have shown that even subtle architectural design flaws can have severe consequences in shared computing environments. For RISC-V, the lack of historical field exposure and a relatively immature security audit ecosystem may present hidden risks.

Although the RISC-V community is developing formal verification tools and secure execution environments (e.g., PMP, enclaves), these features are still nascent compared to Intel’s SGX or AMD’s SEV. China’s domestic chip developers must invest in rigorous security testing and validation frameworks to assure customers of their processors’ trustworthiness—especially in sensitive or regulated sectors.

Strategic Implications

Geopolitics, Industry Disruption, and Global Standards

The rapid development of RISC-V server CPUs in China is not only a technological and industrial phenomenon—it is also deeply strategic. As the global semiconductor industry becomes increasingly enmeshed with geopolitics, national security, and global economic competitiveness, China’s deliberate pivot to RISC-V represents a multidimensional shift with implications far beyond processor design. In this section, we examine the broader strategic consequences of China’s RISC-V trajectory across three critical domains: geopolitical realignment, disruption of existing industry structures, and the evolving landscape of global standards.

Geopolitical Realignment: From Technological Dependence to Digital Sovereignty

In an era defined by digital sovereignty and strategic decoupling, the control over fundamental computing technologies—particularly CPU architectures—has become a central concern for national security policymakers. The U.S.-China technology rivalry has heightened global awareness of vulnerabilities in semiconductor supply chains, many of which are still controlled or influenced by a small number of Western-aligned firms. China’s development of RISC-V server CPUs must be understood within this broader context of geopolitical recalibration.

By investing heavily in RISC-V, China aims to mitigate its dependence on foreign IP and supply chains, particularly in areas vulnerable to export controls or political leverage. As seen in the restrictions imposed on Huawei, SMIC, and other Chinese firms, reliance on foreign-owned architectures such as x86 (Intel, AMD) and ARM (Arm Ltd.) has created systemic exposure for China's technology infrastructure. The licensing models that govern these architectures are subject not only to commercial terms but also to the legal and regulatory frameworks of their host nations—most notably the United States and the United Kingdom.

RISC-V, by contrast, is governed by a global nonprofit organization, RISC-V International, with a decentralized governance model and open-source ethos. While this does not insulate the architecture from geopolitical influence entirely, it provides China with a legally unencumbered alternative to proprietary designs. This enables Chinese firms to innovate, modify, and deploy CPUs without the risk of license revocation or export restriction, and supports Beijing’s strategic goal of creating a self-reliant, indigenous computing stack for critical sectors such as finance, defense, telecommunications, and artificial intelligence.

In addition, the push for RISC-V aligns with China’s broader diplomatic messaging around technological multipolarity—the notion that global technology should not be monopolized by a handful of nations or companies. By promoting RISC-V adoption across Belt and Road Initiative (BRI) partner countries and in forums such as BRICS and the Shanghai Cooperation Organization (SCO), China is actively working to build a coalition of like-minded states seeking alternatives to Western-controlled technology ecosystems.

Industry Disruption: Challenging the x86 and ARM Duopoly

The global server CPU market has historically been dominated by two architectures: x86, primarily represented by Intel and AMD, and ARM, whose designs have proliferated through licensing to hyperscalers (e.g., Amazon Graviton), startups (e.g., Ampere), and mobile-first companies transitioning into the server space. These architectures enjoy robust ecosystems, widespread compatibility, and long-standing customer trust—advantages that will not be easily disrupted.

Nevertheless, the emergence of RISC-V—particularly as driven by China—poses a growing disruption threat to this status quo. As Chinese RISC-V server CPUs mature, they are likely to achieve significant domestic adoption, especially in scenarios where compliance with x86 or ARM licensing conditions is infeasible or undesirable. Government mandates, strategic procurement policies, and “secure compute” programs are likely to drive early demand for RISC-V solutions across China’s public sector and state-owned enterprises.

In time, this domestic base may allow Chinese RISC-V vendors to build scale and operational resilience, positioning them to compete internationally. Although RISC-V is unlikely to displace x86 or ARM entirely in the short term, it could capture meaningful market share in edge computing, custom SoC deployments, AI inference workloads, and sovereign cloud initiatives, particularly in developing countries seeking affordable, non-restricted alternatives to Western chipsets.

Moreover, the economic model behind RISC-V offers cost advantages. Unlike x86 and ARM, which impose per-core or per-device royalties, RISC-V permits free implementation and modification, dramatically lowering the barrier to entry for fabless design houses and vertical integrators. This could unlock a new wave of hardware innovation from smaller players in China and abroad, further fragmenting the traditional CPU landscape.

Importantly, this disruption is not limited to chip vendors. It extends to peripheral markets including motherboard design, datacenter orchestration software, enterprise operating systems, and even cloud management platforms. As China’s RISC-V ecosystem grows, it will demand a parallel development of supporting infrastructure that can challenge incumbent supply chains and alter purchasing patterns globally.

Standardization and Global Governance: A Contest for Control

The expansion of China’s influence within the RISC-V community also introduces questions about the governance of open-source standards and the geopolitical neutrality of technical bodies. As China’s investment in RISC-V accelerates, so too does its representation in RISC-V International and its working groups, which govern the development of ISA extensions, compliance frameworks, and certification processes.

Several of China’s leading institutions—including the Chinese Academy of Sciences, Alibaba’s T-Head, and PLCT Lab—have submitted proposals to extend the base RISC-V ISA for server workloads, AI processing, and secure enclave functionality. While these contributions reflect genuine innovation, they have sparked concern among some international stakeholders about the potential for nationalized standard-setting, particularly if consensus mechanisms are overridden by geopolitical agendas.

In response, some Western observers have proposed stricter governance models, geographic segmentation of standard development, or even the creation of “clean rooms” for RISC-V standards separate from perceived political influence. While these measures have not been implemented, they underscore the growing tension between openness and strategic alignment in the governance of foundational technologies.

The outcome of this contest could determine whether RISC-V remains a truly global standard or bifurcates into region-specific variants—one aligned with Chinese industrial policy and the other with Western regulatory and commercial interests. Such a scenario would mirror the current fragmentation in 5G, cloud computing, and AI governance, further complicating global interoperability and supply chain integration.

Long-Term Outlook: A Multipolar CPU Future

Looking forward, the strategic implications of China’s RISC-V push suggest that the global computing landscape is entering a multipolar phase. Rather than converging on a single dominant architecture, the world is likely to witness the coexistence of multiple CPU paradigms, each rooted in different legal, political, and economic foundations.

In this new landscape, RISC-V may not immediately dominate in raw performance or market share, but it will play a crucial strategic role—especially for countries seeking alternatives to proprietary architectures and politically conditioned IP access. China’s leadership in this space, underpinned by state coordination, industrial capacity, and long-term vision, positions it to shape the rules, infrastructure, and adoption patterns of open hardware well into the next decade.

The Road Ahead for China’s RISC-V Server Chips

The emergence of China as a central player in the global RISC-V movement marks a pivotal turning point in the evolution of modern computing. Nowhere is this transformation more evident than in the realm of server-class processors, a category historically dominated by proprietary architectures and global incumbents. As outlined throughout this analysis, China's pursuit of RISC-V server CPUs is not merely a technological experiment—it is a comprehensive national strategy aimed at recalibrating the country’s position in the digital hierarchy.

At the heart of this movement lies a multifaceted rationale. The adoption of RISC-V offers China an opportunity to circumvent longstanding dependencies on foreign-owned architectures, particularly x86 and ARM, which are increasingly viewed through the lens of geopolitical risk. In a world where export controls, licensing suspensions, and compliance regimes have become tools of statecraft, open-source hardware represents a path toward unencumbered technological autonomy. For China, the stakes are especially high: access to secure, high-performance server CPUs is essential for the operation of sovereign cloud systems, critical infrastructure, and national AI initiatives.

To meet these strategic goals, China has mobilized a broad coalition of actors, spanning academia, industry, and government. Initiatives such as Alibaba’s Xuantie processor family, XiangShan’s open-source microarchitecture projects, and StarFive’s edge-oriented CPUs are not isolated ventures. They represent the forward edge of a nationally coordinated effort to build a comprehensive RISC-V server CPU ecosystem. Complementing these efforts is a growing suite of software tools, development platforms, and operating systems that are being adapted to support RISC-V, thereby addressing one of the architecture’s historic weaknesses: ecosystem maturity.

Despite these encouraging developments, significant challenges remain. As highlighted in previous sections, China’s RISC-V server CPUs still lag behind x86 and ARM processors in several key performance and scalability metrics. Synthetic benchmarks reveal gaps in single-threaded performance, memory latency, virtualization efficiency, and multi-core throughput. These gaps are partially attributable to architectural immaturity but are also compounded by fabrication constraints, notably the country’s limited access to cutting-edge manufacturing nodes such as 5nm and below.

Furthermore, software remains a persistent bottleneck. While strides have been made in compiler development, OS compatibility, and cloud integration, the absence of enterprise-grade support from major global vendors continues to hinder commercial adoption outside state-mandated projects. Compatibility with legacy enterprise workloads—many of which are optimized for x86—and the lack of complete parity in tools such as hypervisors, orchestration platforms, and security frameworks remain formidable barriers to widespread deployment.

Nevertheless, the long-term trajectory of China’s RISC-V strategy appears robust. Several factors support this conclusion. First, the sheer volume of investment, both public and private, is accelerating design iteration, talent development, and IP accumulation. Second, the nature of the RISC-V architecture itself—modular, open, and extensible—allows for greater adaptability over time, enabling China to tailor instruction set extensions to local performance needs. Third, geopolitical necessity ensures that the push for RISC-V will not abate, even in the face of technical or commercial headwinds.

In strategic terms, China’s RISC-V efforts also serve as a catalyst for global realignment. The rise of an alternative CPU architecture with significant state backing from the world’s second-largest economy introduces a structural divergence in the international technology ecosystem. If successful, China’s RISC-V platforms could catalyze a new generation of non-aligned computing infrastructure—particularly in countries seeking to reduce their dependence on Western IP or to build sovereign digital capabilities. This has important implications for the global semiconductor industry, including shifts in supply chain patterns, IP licensing models, and standardization governance.

From the perspective of multinational technology companies, the maturation of China’s RISC-V capabilities presents both a challenge and an opportunity. On the one hand, the proliferation of a new hardware platform introduces competitive disruption, potentially eroding the market share of entrenched architectures. On the other hand, it invites new forms of collaboration, particularly around open-source development, cross-border IP co-creation, and software enablement. For Western firms willing to navigate the complex regulatory landscape, partnerships with China’s RISC-V ecosystem may offer long-term strategic dividends.

Looking forward, several scenarios emerge for the future of China’s RISC-V server CPUs:

- Accelerated Adoption Scenario: If China can rapidly close the performance and software gaps—possibly through access to advanced node manufacturing or successful standardization of domestic software stacks—RISC-V server CPUs could become a mainstream choice in both public and private sector deployments. This would position China as a global leader in open hardware innovation.

- Fragmented Adoption Scenario: In this trajectory, RISC-V gains traction primarily in niche or sovereign use cases (e.g., government clouds, AI inference clusters) but fails to break into mainstream enterprise markets due to ecosystem inertia and persistent compatibility issues. Nevertheless, it becomes a viable third option in a tri-polar CPU world.

- Stalled Progress Scenario: In the event of sustained technical, logistical, or political roadblocks—such as continued lack of EUV access or intensified sanctions—China’s RISC-V efforts could lose momentum. In this case, the architecture might remain peripheral, overshadowed by ARM’s licensing flexibility and x86’s entrenched dominance.

The most likely outcome lies between the first two scenarios. Given the momentum behind current initiatives, the global push for architectural diversity, and the rising costs of proprietary IP, RISC-V—particularly as championed by China—is poised to play a transformative role in the future of server computing. It may not displace existing incumbents entirely, but it will certainly redefine the boundaries of possibility in processor innovation.

In conclusion, China’s commitment to developing RISC-V server CPUs is a reflection of its broader ambitions to lead in the next wave of digital infrastructure. It is a long-term bet, grounded in the principles of openness, autonomy, and resilience. Whether viewed through the lens of national strategy, industrial policy, or technological innovation, it is clear that RISC-V is no longer an experimental architecture on the periphery of computing. In China, it is becoming a central pillar of the nation's plan to shape the future of global computing on its own terms.

References

- RISC-V International – Open Standard for a Free and Open ISA

https://riscv.org - Alibaba T-Head – Xuantie RISC-V Core Series

https://www.alibabacloud.com/blog/introduction-to-the-xuantie-risc-v-cpu-series_599059 - Institute of Computing Technology – XiangShan Project

https://xiangshan.ict.ac.cn - StarFive – VisionFive and Dubhe RISC-V Processors

https://www.starfivetech.com - Semiconductor Manufacturing International Corporation (SMIC)

https://www.smics.com - CHIPS and Science Act – U.S. Department of Commerce

https://www.commerce.gov/chips - OpenEuler: Huawei's Open Source OS with RISC-V Support

https://openeuler.org/en - China’s 14th Five-Year Plan Summary – Center for Strategic and International Studies (CSIS)

https://www.csis.org/analysis/chinas-14th-five-year-plan - RISC-V Summit Asia – Keynotes and Presentations

https://riscv.org/event/risc-v-summit-asia - Linux Foundation: State of RISC-V Ecosystem Report

https://www.linuxfoundation.org/resources/publications/risc-v